AMD第3代EPYC™產品陣容的最新成員配備768MB的L3快取,具有立即運行(drop-in)的平台相容性以及現代安全功能

EPYC處理器的技術運算產業體系隨著各大OEM、ODM、SI、ISV以及雲端業者的解決方案共同蓬勃發展

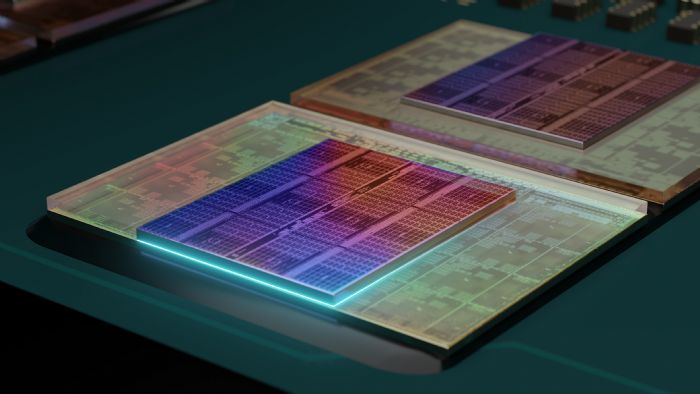

台北—2022年3月22日—AMD(NASDAQ: AMD)宣布推出全球首款採用3D晶片堆疊技術(3D die stacking)的資料中心CPU─代號為“Milan-X”、採用AMD 3D V-Cache™技術的AMD第3代EPYC™處理器。全新處理器基於“Zen 3”核心架構,進一步擴大了第3代EPYC CPU產品陣容,與沒有採用堆疊技術的AMD第3代EPYC處理器相比,可以為各種目標技術運算工作負載提供高達66%的效能提升註1,2。

全新處理器擁有領先業界的L3快取註3,並具備與第3代EPYC CPU相同的插槽、軟體相容性以及現代安全功能,同時為計算流體力學(CFD)、有限元素分析(FEA)、電子設計自動化(EDA)以及結構分析等技術運算工作負載提供卓越效能。這些工作負載對於必須對複雜的實體世界進行建模以創建模型的公司來說,是關鍵的設計工具,協助他們為世界上最創新的產品進行工程設計測試與驗證。

AMD全球資深副總裁暨伺服器事業群總經理Dan McNamara表示,承襲我們在資料中心的發展動能以及業界首創的歷史,採用AMD 3D V-Cache技術的AMD第3代EPYC處理器展現了我們領先的設計與封裝技術,使我們能夠帶來業界首款採用3D晶片堆疊技術且專為工作負載量身打造的伺服器處理器。我們採用AMD 3D V-Cache技術的最新處理器為關鍵任務技術運算工作負載提供突破性的效能,帶來更好的設計產品並加快上市時程。

美光資深副總裁暨運算和網路事業部總經理Raj Hazra表示,隨著客戶越來越廣泛採用資料密集應用程式,資料中心的基礎架構方面也有新的需求。美光與AMD的共同願景是為高效能資料中心平台提供領先的DDR5記憶體的完整能力。我們與AMD的深度合作包括美光最新DDR5解決方案能支援AMD平台,以及將採用AMD 3D V-Cache技術的AMD第3代EPYC處理器導入我們的資料中心。我們已經看到在執行特定EDA工作負載時,與未採用AMD 3D V-Cache技術的AMD第3代EPYC處理器相比,效能提升了高達40%。

領先業界的封裝技術創新

快取大小的提升一直以來都是改進效能的重中之重,尤其是重度依賴龐大資料集的技術運算工作負載。這些工作負載受益於快取大小的提升,然而2D晶片設計對於CPU上可有效建構的快取容量有著物理上的限制。AMD 3D V-Cache技術透過將AMD “Zen 3”核心與快取模組結合來克服這些物理挑戰,不僅增加L3快取容量,還最大程度降低延遲並提高吞吐量。這項技術象徵CPU設計與封裝的一大創新,在目標技術運算工作負載中實現突破性的效能。

突破性效能

作為全球效能最強大、適用於技術運算的伺服器處理器註4,採用AMD 3D V-Cache技術的AMD第3代EPYC處理器在執行目標工作負載時,能夠提供更快的結果效率,例如:

• 電子設計自動化(EDA)-與EPYC 73F3 CPU相比,16核心的AMD EPYC™ 7373X CPU在Synopsys VCS™提供高達66%的模擬速度提升註5。

• 有限元素分析(FEA)-與競爭對手的頂尖處理器相比,64核心的AMD EPYC 7773X處理器在Altair® Radioss®模擬應用程式的效能平均提高44%註6。

• 計算流體力學(CFD)-與競爭對手的32核心處理器相比,32核心的AMD EPYC 7573X處理器在執行Ansys® CFX®時,每天可解決的CFD問題數量平均高出88%註7。

這些效能與功能最終能讓客戶在資料中心縮減部署的伺服器數量並降低功耗,從而降低總擁有成本(TCO)、減少碳排放並達成永續環保的目標。舉例來說,在Ansys® CFX® cfx-50測試每天執行4600個作業的典型資料中心場景中,與競爭對手最新基於2P 32核心處理器的伺服器相比,基於2P 32核心AMD EPYC 7573X CPU的伺服器可將所需伺服器部署數量從20台大幅縮減到10台,功耗也降低49%。這些優勢預計將在3年內使TCO減少51%。

換而言之,在資料中心部署選用搭載AMD 3D V-Cache的AMD第3代EPYC處理器,能發揮環境永續效益,相當於每年減少超過81英畝美國森林的碳吸存量註8。

採用AMD 3D V-Cache技術的AMD第3代EPYC處理器產品規格

核心數 型號 CCD

數量 TDP

(瓦) cTDP範圍(瓦) 基礎頻率(GHz) 最高提升頻率

(高達GHz)註9 L3快取

(MB) DDR

通道 每千片價格

(美元)

64 7773X 8 280 225-280 2.20 3.50 768 8 8,800美元

32 7573X 8 280 225-280 2.80 3.60 768 8 5,590美元

24 7473X 8 240 225-280 2.80 3.70 768 8 3,900美元

16 7373X 8 240 225-280 3.05 3.80 768 8 4,185美元

全面的產業體系支援

採用AMD 3D V-Cache技術的AMD第3代EPYC處理器即日起搭載於各大OEM廠商的系統,包括Atos、思科、戴爾科技集團、技嘉、HPE、聯想、雲達科技(QCT)以及美超微(Supermicro)。

採用AMD 3D V-Cache技術的AMD第3代EPYC處理器亦獲得AMD軟體產業體系合作夥伴的廣泛支援,包括Altair、Ansys、Cadence、達梭系統(Dassault Systèmes)、西門子以及新思科技。

Microsoft Azure HBv3虛擬機器現已全面升級至採用AMD 3D V-Cache技術的AMD第3代EPYC。微軟表示,HBv3虛擬機器是Azure HPC平台有史以來部署速度最快的產品,與先前的HBv3系列虛擬機器相比,搭載AMD 3D V-Cache的虛擬主機在執行關鍵HPC工作負載的效能提升高達80%。

請至此連結觀看發表影片,並至官網查看採用AMD 3D V-Cache技術的AMD第3代EPYC處理器。如欲瞭解更多訊息並閱讀AMD客戶的使用心得,請參閱此連結。

相關資源

• 更多關於:採用AMD 3D V-Cache技術™的AMD EPYC™處理器

• 更多關於:AMD EPYC™處理器

• Twitter:於@AMD追蹤AMD新訊

• LinkedIn:AMD LinkedIn

關於AMD

50多年來,AMD(NASDAQ:AMD)推動創新高效能運算、繪圖及視覺技術。全球數十億的消費者、世界500強企業以及尖端科學研究機構皆仰賴AMD的技術來改善生活、工作及娛樂。AMD員工致力於研發領先的高效能與自行調適產品,不斷突破技術的極限。欲瞭解AMD如何成就今天,啟發未來,請瀏覽AMD網站、部落格、LinkedIn及Twitter。

©2022年,AMD公司版權所有。AMD、AMD箭頭、EPYC、AMD 3D V-Cache及上述名稱的組合為AMD公司的商標。

採用AMD 3D V-Cache技術的AMD第3代EPYC處理器為技術運算工作負載挹注領先業界的卓越效能

避免法律糾紛,轉載本區文稿請先徵得原作者同意!

文章回應

目前尚無回應,成為第一個回應的人吧!

回應本篇文章!

(以下回應不會連結到FaceBook)(言責自負,請勿涉及人身攻擊,以免挨告!)

尚未 登入會員 ,無法回應!